DDR4 と DDR5: 基本周波数を見ると最大 2 倍のパフォーマンス

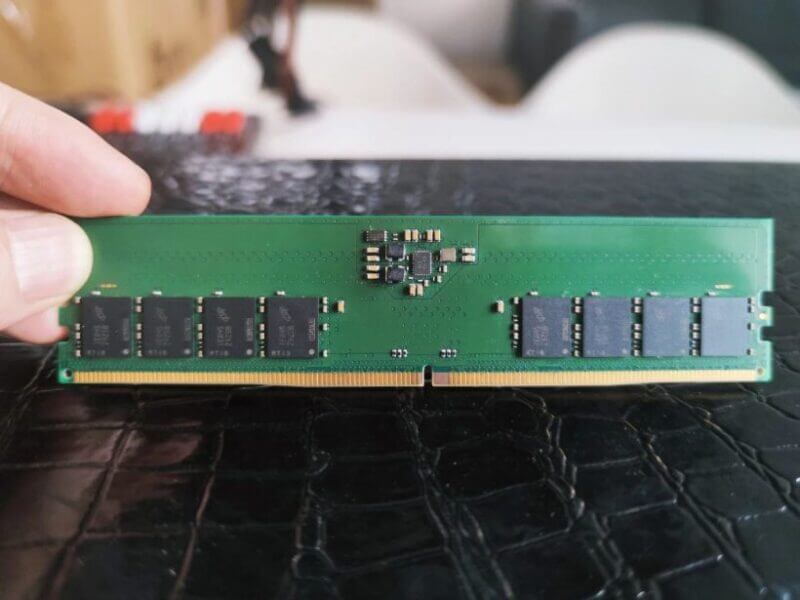

この新しい DDR 標準( JEDEC の定義を担当) によってもたらされる最初の改善により、 64 ビット リンクでは最大 1.1 ボルトの電圧での動作が可能になり、 16 および 8 ビット リンクでは 1.2 ボルトに達することが可能になります。これに加えて、モジュールには独自の電圧レギュレータが含まれ、現在のものよりもマザーボードからの独立性が高くなります。

DDR5 互換マザーボードが受け入れるメモリ サイズも増加し、 12 チャネルから 16 チャネルになります。これにより、メインコンシューマボードの現在の 64 GB 制限から128 GB の RAM まで拡張できるようになります。安定性とオーバークロック能力も向上し、市場のさまざまなRAM モジュールの影響を非常に受けやすい AMD Ryzen プロセッサーに恩恵をもたらします。

DDR5 は現在、大量のランダム メモリが求められているビジネス分野を念頭に置いて開発されています。 16 Gbpsチップでは密度が増加し、同じモジュール内でより高い密度を達成できるようになります。メモリ消費量を削減することも優先目標です。

2019年にまずサーバーとデータセンターに到達し、2020年に残りの消費者に到達する予定です。

ただし、これらの改善にはすべて、遅延が増加するという欠点が生じます。これは周波数を上げることで補われます。 DDR5 RAM の JEDEC 仕様は4800 MHz ベースであり、このテクノロジが通常、長年にわたってどれほど改善されているかを知ると、多くの努力なしで最大6400 MHzの周波数を達成できると推定されています。

現在、ケイデンスやマイクロンなどのメーカーは、サーバーやデータセンターから始めて来年からこれらのメモリの製造を開始することを検討している。残りの消費者については、2020 年までもう少し待たなければなりません。その日、AMDはZenアーキテクチャに終止符を打つため、次のアーキテクチャはすでにDDR5メモリを念頭に置いて作られている可能性が高い。